1965

# **315** Electronic Data Processing System

A Marketing Services Educational Publication

HARDWARE (Operating - Processor)

November 65 ST-5008-15

# NCR EDP INFORMATION

HARDWARE (OPERATING -PROCESSOR)

page: 1 of 39 date: Nov. 65

number: 1

ST-5008-15

A Marketing Services Educational Publication

TITLE -- CENTRAL PROCESSOR (315, 315-100)

General Description

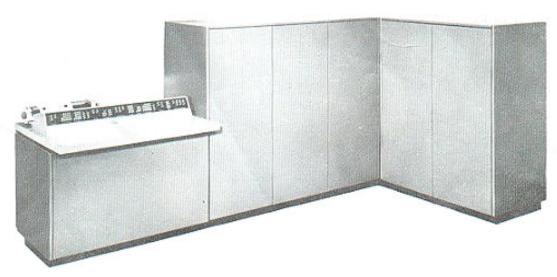

315 Data Processor

The 315 and 315-101 Central Processor contains the following elements:

- · Central Console

- · Control unit

- · Arithmetic unit

- · Memory section

Both numeric and alphabetic information may be handled by the Processor. The basic information unit is called a slab which consists of 12 bits plus a parity bit. The external Main Memory is available in many sizes as follows: 5,000, 10,000, 15,000, 20,000, 30,000 or 40,000 slabs.

The memory provides the storage for the program and is used for the temporary storage of data during computation and processing. The Processor executes instructions and controls the flow of data between memory and the associated peripheral units. No restriction is made on the assignment of memory locations for the program or data. Information is transferred to and from the memory by slab. The arithmetic unit also processes data by the complete slab.

The arithmetic unit called the Adder adds two 12-bit slabs in parallel. These two slabs may be added in one of the following 5 ways:

- Decimal Addition in groups of four bits, with carries between all bits and between the three groups of four bits.

- Decimal Subtraction in groups of four bits, with carries between all bits and between the groups of four bits.

- Binary Addition with carries over the full twelve bits.

- Binary Addition with carries over two groups of six bits, but no carry between the sixth and the seventh bits.

- · Binary Subtraction with carries over the full twelve bits.

These are not necessarily direct command functions i.e., BADD, but are used by other commands such as compare, count, scan and register and address modification in any command.

An integral part of the Processor is a magnetic core memory referred to as the Auxiliary Memory. Containing special registers which are accessible by special commands and used for relative addressing procedures. Auxiliary memory consists of 64 registers that have 18 bits plus 1 parity bit; an accumulator of 8 slabs, each containing 12 bits plus parity.

In order to access 40,000 slabs of memory (00,000 to 39,999) an 18-bit address is required. This address consists of 4 full digits with 4 bits each, and an additional 2 bits for the most significant digit with a range of 0 through 5.

## Instruction Format

The 315, 315-100 systems function primarily as single address processors. A few commands are capable of referring to two addresses at the same time for the purpose of transferring information from one main memory location to another. However, only one operand at a time is accessed by an arithmetic command.

For example, if the contents of memory address 100 are added to the contents of memory address 150, and the sum is stored in memory address 200, three commands must be executed.

- The LOAD command to load the contents of address 100 into the accumulator for temporary storage.

- The ADD command to add the contents of address 150 to the contents of the accumulator. The sum is retained in the accumulator.

- The STORE command to store the contents of the accumulator in address 200.

Addition of the two numbers is performed in the diode logic adder, but the accumulator provides temporary storage for the intermediate and final results.

# NCR 315 CODE CHART

| ZONE |      |      |      |      |      |      |      | NUMER | IC BITS |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|-------|---------|------|------|------|------|------|------|------|

| BITS | 0000 | 0001 | 0010 | 1100 | 0100 | 0101 | 9110 | 0111  | 1000    | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| 00.  | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7     | 8       | 9    | @    | ,    | Ø    | &    |      | _    |

| 01   | 1    | A    | В    | С    | D    | E    | F    | G     | Н       | L    | ;    | **-  | ?    | :    | -    | 1    |

| 10   | +    | 1    | K    | L    | M    | N    | 9    | Р     | Q       | R    | %    | =    | \$   | (    | )    | /    |

| 11   | *    | #    | S    | Т    | U    | ν    | W    | Х     | Υ       | Z    | <    | >    | 1    | С    | ]    | 1    |

| ABSOLUTE | X | хF | С | ; A , |

|----------|---|----|---|-------|

| FORMAT   | Υ | ,Q | G | В     |

| DRINTED DEDRECENTATION       |   | OVE | RPRINTE | D WIT | н д "- | +" SY | MBOL |   |

|------------------------------|---|-----|---------|-------|--------|-------|------|---|

| PRINTER REPRESENTATION<br>OF | M | N   | 0       | Р     | U      | v     | W.   | X |

| "NON-PRINTING" CHARACTERS    | ? | :   | +       | *     |        | Г     | 3    | 1 |

|   |   | × | Fo | y C | } |   |   |

|---|---|---|----|-----|---|---|---|

| 0 | 1 | 2 | 3  | 4   | 5 | 6 | 7 |

| 8 | 9 | @ |    | 奶   | & |   | - |

| X or Y   | 0  | 1  | 2  | 3  | 4  | 5   | 6  | 7  | 8  | 9  | @  | ,  | Ø  | 8. |    | -  |

|----------|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|

| REGISTER | 00 | 01 | 02 | 03 | 04 | 05  | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 |

| NUMBER   | 16 | 17 | 18 | 19 | 20 | -21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

\*Trade Mark

#### Single Stage Instruction

Add Instruction ...

OP CODE 1 3 03

Example ...

Add the contents of memory address 03 999 and 04 000 to the contents of the Accumulator and store result temporarily in the Accumulator.

IR 3 originally contained 03 000.

#### NEAT

| OP  | V | L  | х  | OPERAND |

|-----|---|----|----|---------|

| ADD |   | 02 | 03 | 999     |

## ABSOLUTE

| X | OP | A   |

|---|----|-----|

| 2 |    | 0 0 |

## BCD [INTERNAL]

| X    | × | OF  | >      |      | Α    |      |

|------|---|-----|--------|------|------|------|

| 0011 | 0 | 001 | , 0011 | 1001 | 1001 | 1001 |

| R#   | GR  | F | C   |   | Α   | 1   |

|------|-----|---|-----|---|-----|-----|

| IR 3 | 1 1 | 1 | 1 3 | 9 | 1 9 | , 9 |

Double Stage Instruction

Count (CNT) Instruction ...

F C Q G OP Code 1 0 0 0 10

Example...

Add 1 to IR7, then compare result with the value stored in memory locations  $03\,999$  and  $04\,000$ .

IR3 originally contained 03 000

#### NEAT

|     |   |   |     | 0   | PERAND |   |

|-----|---|---|-----|-----|--------|---|

| OP  | V | L | X   | Α   | B      | Y |

| CNT |   |   | 0.3 | 000 |        | 7 |

# ABSOLUTE

| X   | C   | P   |   | Α |     |     | Υ   | . 2. 4 |   | В   | 9   |

|-----|-----|-----|---|---|-----|-----|-----|--------|---|-----|-----|

| 3 , | , 1 | , 0 | 9 | 9 | , 9 | 7 . | . 0 | , 0    | 0 | . 0 | . 1 |

# BCD [INTERNAL]

| Х    | ×   | OP   | A                  | Y    | Y  | Q   | G    | В                  |

|------|-----|------|--------------------|------|----|-----|------|--------------------|

| 0011 | 0,0 | 0000 | 1001   1001   1001 | 0111 | 0, | 000 | 0000 | 0000 , 0000 , 0001 |

| R# GRIF    | c l | A         | R# GR Q  | G   | В     |

|------------|-----|-----------|----------|-----|-------|

| IR 3, , 1, | 0   | 9 1 9 1 9 | IR 7 , 0 | 0 0 | 0 , 1 |

| INSTRUCTION<br>GROUP | OP/V<br>MNEMONIC | CODE<br>F C Q G | N-REG<br>SETTING | INSTRUCTION<br>GROUP | OP/V<br>MNEMONIC | FCQG    | N-REG<br>SETTING |

|----------------------|------------------|-----------------|------------------|----------------------|------------------|---------|------------------|

| LOAD                 | *LD:             | 1               | 0.1              | JUMP                 | JUMP; I          | 6 Ø     | 1 4              |

| STORE                | *sT:             | 2               | 0.2              | JUMP                 | JUMP: IP         | 7 💆     | 1 4              |

| ADD                  | * ADD:           | 3               | 0.3              | JUMP                 | **MLRA;          | 6 Ø     | 1.4              |

| SUBTRACT             | *sus:            | 4               | 0.4              | JUMP                 | **SKIP;          | 7 Ø     | 1.4              |

| MULTIPLY             | *MULT:           | 5               | 0.5              | EDIT                 | EDIT:            | &       | 1 5              |

| COMPARE              | *COMP:           | 6               | 0.6              | SUPPRESS             | SUPP;            |         | 1 6              |

| TEST                 | TEST: G          | 0 7             | 0.7              | COUNT                | *CNT:            | 1 0     | 2 1              |

| TEST                 | TEST; L          | 1 7             | 0.7              | MODIFY               | LD: R            | 2 0 0 0 | 2 2              |

| TEST                 | TEST: E          | 2 7             | 0.7              | MODIFY               | LD; J            | 2 0 0 1 | 2 2              |

| TEST                 | TEST: -          | 3 7             | 0.7              | MODIFY               | SLD:R            | 2002    | 2 2              |

| TEST                 | TEST: 0          | 4 7             | 0.7              | MODIFY               | SLD; J           | 2003    | 2.2              |

| TEST                 | JUMP:            | 5 7             | 0.7              | MODIFY               | MOVE: RR         | 2004    | 2.2              |

| TEST                 | TEST: D          | 6 7             | 0.7              | MODIFY               | MOVE: JR         | 2005    | 2 2              |

| TEST                 | TEST: T          | 7 7             | 0.7              | MODIFY               | MOVE: RJ         | 2006    | 2 2              |

| TEST                 | **DIR            | 0 7             | 0.7              | MODIFY               | MOVE: JJ         | 2007    | 2 2              |

| TEST                 | **SETF:+         | 1 7             | 0.7              | MODIFY               | ST; R            | 2008    | 2 2              |

| TEST                 | **SETF:0         | 2 7             | 0.7              | MODIFY               | ST; J            | 2009    | 2.2              |

| TEST                 | **SETF:-         | 3 7             | 0.7              | MODIFY               | AUG: R           | 2010    | 2 2              |

| TEST                 | **SETF: D        | 6 7             | 0.7              | MODIFY               | AUG: J           | 2011    | 2 2              |

| TEST                 | **SETF: T        | 7 7             | 0.7              | MODIFY               | SAUG: R          | 2012    | 2 2              |

| SHIFT                | *SHFT: AR        | 0 8             | 10               | MODIFY               | SAUG: J          | 2013    | 2 2              |

| SHIFT                | *SHFT: DR        | 1 8             | 10               | MOVE                 | MOVE; B          | 300     | 2 3              |

| SHIFT                | *SHFT: RR        | 2 8             | 10               | MOVE                 | MOVE; E          | 3 0 1   | 2 3              |

| SHIFT                | *SHFT: DL        | 3 8             | 10               | MOVE                 | **SPRD: 8        | 300     | 2.3              |

| SHIFT                | *SHFT: RC        | 4 B             | 10               | MOVE                 | **SPRD; E        | 3 0 1   | 2 3              |

| SHIFT '              | *SHFT: LC        | 6 B             | 1.0              | SCAN                 | SCND; GV         | 4 0 V 1 | 2.4              |

| SHIFT                | *SHFT: AL        | 7 8             | 10               | SCAN                 | SCND: LV         | 40 V 2  | 2.4              |

| ADD TO MEMORY        | *ADD: M          | 9               | 1.1              | SCAN                 | SCND: EV         | 4 0 V 4 | 2.4              |

| BINARY ADD           | *BADD:           | @               | 1.2              | SCAN                 | SCNA: GN         | 4 0 M 9 | 2 4              |

| DIVIDE               | *DIV:            | ν,              | 1.3              | SCAN                 | SCNA: LÑ         | 4 0 M@  | 2 4              |

| JUMP.                | TEST: LH         | o Ø             | 1.4              | SCAN                 | SCNA: EÑ         | 4 0 M   | 2.4              |

| JUMP                 | TEST: RH         | 1 🗹             | 1.4              | PACK                 | LDAD:            | 500     | 2.5              |

| JUMP                 | SETF: LH         | 2 🛮             | 1.4              | PACK                 | LDAD; XR         | 501     | 2 5              |

| JUMP                 | SETF: RH         | 3 Ø             | 1.4              | PACK                 | LDAD: XL         | 502     | 2 5              |

| JUMP                 | CLRF: LH         | 4 Ø             | 1.4              | PACK                 | LDAD: XB         | 503     | 2 5              |

| JUMP                 | CLRF; RH         | 4 Ø             | 14               |                      | March L          | CONT'D  |                  |

|                      | *R = 15 OR       | ≠ 15            |                  |                      | v = 1−7          |         |                  |

| NCR 315 INSTRUCTION | GROUPS,  | MNEMONICS,   | CODES | AND |

|---------------------|----------|--------------|-------|-----|

| CORRESPONDING       | G N-REGI | STER SETTING | GS    |     |

| INSTRUCTION | MNEMONIC  | F C Q G | N-REG<br>SETTING | INSTRUCTION<br>GROUP | MNEMONIC | FCQG    | N-REG<br>SETTING |

|-------------|-----------|---------|------------------|----------------------|----------|---------|------------------|

| PUTAWAY     | STDA;     | 6 0 0   | 2 6              | DUFFER               | STRT: S  | 3 - 0   | 3 3              |

| PUTAWAY     | PAST; XR  | 6 0 1   | 2 6              | BUFFER               | RCK:     | 3 1     | 3 3              |

| PUTAWAY     | PAST; XL  | 6 0 2   | 2 6              | BUFFER               | PKT:     | 3 - 2   | 3 3              |

| PUTAWAY     | PAST; XB  | 6 0 3   | 2 6              | BUFFER               | STOP: S  | 3 - 3   | 3 3              |

| INTERROGATE | SELC; DN  | 7 0 0 0 | 2 7              | BUFFER               | PRNT:    | 3 - 4   | 3 3              |

| INTERROGATE | SELC; DP  | 7 0 0 1 | 2.7              | BUFFER               | PNCH:    | 3 - 4   | 3 3              |

| INTERROGATE | *SELC: R  | 7 0 0 2 | 2.7              | MAG. TAPE            | RMT;     | 4 - 0 6 | 3 4              |

| INTERROGATE | *SELC: T  | 7003    | 2 7              | MAG. TAPE            | WMT:     | 4 - 1 G | 3.4              |

| INTERROGATE | *TEST: SW | 7 0 1 0 | 2 7              | MAG. TAPE            | BACK;    | 4 - 2 6 | 3 4              |

| INTERROGATE | *SELP;    | 7 0 1 1 | 2 7              | MAG. TAPE            | WIND;    | 4 - 3 6 | 3.4              |

| INTERROGATE | *SELS:    | 7 0 1 2 | 2.7              | MAG. TAPE            | WIND; L  | 4 - 4 6 | 3 4              |

| INTERROGATE | *SELQ;    | 7 0 t 3 | 2 7              | MAG. CARD            | RCC      | 5 - 0 6 | 3.5              |

| INTERROGATE | *CLRU; C  | 7 0 2 0 | 2.7              | MAG. CARD            | wcc      | 5 - 1 G | 3.5              |

| INTERROGATE | *CLRU; P  | 7 0 2 1 | 2 7              | INQUIRY              | RQ       | 6 - 0   | 3 6              |

| INTERROGATE | *CLRU; S  | 7 0 2 2 | 2 7              | INQUIRY              | WQ       | 6 - 1   | 3 6              |

| INTERROGATE | *CLRU; Q  | 7 0 2 3 | 2.7              | INQUIRY              |          |         |                  |

| INTERROGATE | *SETU; C  | 7 0 3 0 | 2.7              |                      | -        |         | . 3              |

| INTERROGATE | *SETU: P  | 7031    | 2 7              |                      |          |         |                  |

| INTERROGATE | *SETU;S   | 7 0 3 2 | 2.7              |                      |          |         |                  |

| INTERROGATE | *SETU:Q   | 7033    | 2 7              |                      | 4.3      |         |                  |

| PLACE       | HALT; D   | 1 - 0   | 3 1              |                      |          |         |                  |

| PLACE       | HALT: A   | 1 - 1   | 3 1              |                      |          |         |                  |

| PLACE       | TYPE; D   | 1 - 2   | 3 1              |                      |          |         |                  |

| PLACE       | TYPE: A   | 1 - 3   | 3 1              |                      |          |         |                  |

| PLACE       | PPT; C    | 1 - 4   | 3.1              |                      |          |         |                  |

| PLACE       | PPT:S     | 1 - 5   | 3.1              |                      |          |         |                  |

| PLACE       | TYPE: AP  | 1 - 7   | 3 1              |                      |          |         |                  |

| READER      | RPT: S    | 2 - 1   | 3 2              |                      |          |         |                  |

| READER      | RPT: C    | 2 - 2   | 3 2              |                      |          |         | i i              |

| READER      | RPT: CX   | 2 - 3   | 3 2              |                      |          |         |                  |

| READER      | RCOL: F   | 2 - 4   | 3 2              |                      |          |         | 100              |

| READER      | RCOL:     | 2 - 5   | 3 2              |                      |          |         |                  |

| READER      | RCOL; TF  | 2 - 6   | 3 2              |                      |          |         |                  |

| READER      | RCOL; T   | 2 - 7   | 3 2              |                      |          |         | 1 b              |

## Operator Control Console

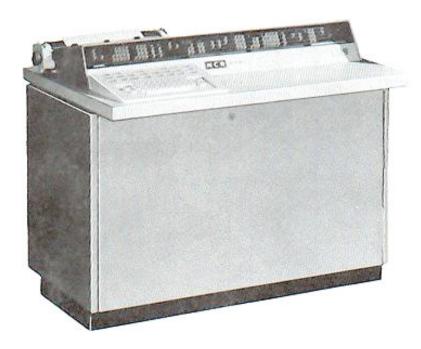

The Control Console is part of the Processor and gives the operator a means of controlling the 315 system. Illustrated below is the console which consists of a typewriter, control buttons, and indicators.

315 Control Console

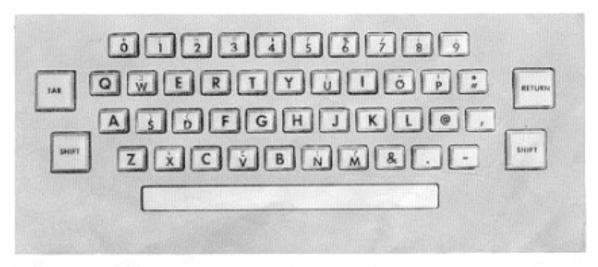

# Console Typewriter

The electric typewriter provides direct communication with the Processor memory. Data may be entered into the memory through the keyboard, or the Processor can transmit data to the typewriter for output through the typewriter printer. The console typewriter allows the operator to interrogate the memory, modify a program, and to note the various conditions of the program during a production run.

#### Control Keys

As shown below, the typewriter keyboard contains TAB, RETURN, and SHIFT keys. These keys affect the typewriter only, therefore no input is made to the Processor.

The TAB key moves the carriage to a tabulator stop which had previously been set by the engineer or operator.

The RETURN key causes the carriage to return to the left margin and advance the paper from one to three lines. The typewriter is often used by the programmer to type a message which indicates information to the operator. If the programmer has not included a carriage return in the coding, the operator must manually press RETURN. There is no automatic return at the end of a typed line.

The two SHIFT keys determine whether the upper or lower position of the key is to be typed. For example, in the lower shift the character "6" will be printed; however, in the upper shift the character "%" will be printed. When a message is typed from the Processor, the shift position is automatically determined.

NOTE: When the typewriter is in the upper shift position only the keys where two terms (a symbol and an alpha, or a symbol and a digit) appear on one key, are operable.

#### Character Keys

There are 63 character keys and a space bar. When the space bar is pressed, the binary configuration 001100 is transmitted to the Processor. The paper in the typewriter will show only a blank space. The character keys permit addressing or accessing any location in memory, and the entry into the Processor may be any of the 63 six-bit characters.

Typewriter Keyboard

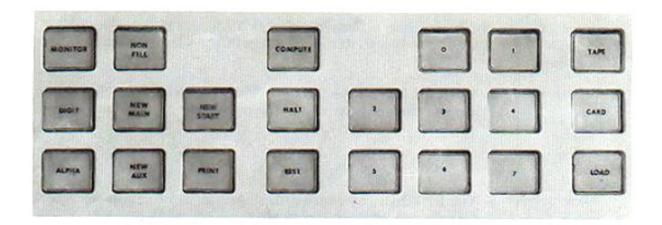

Console Control Buttons

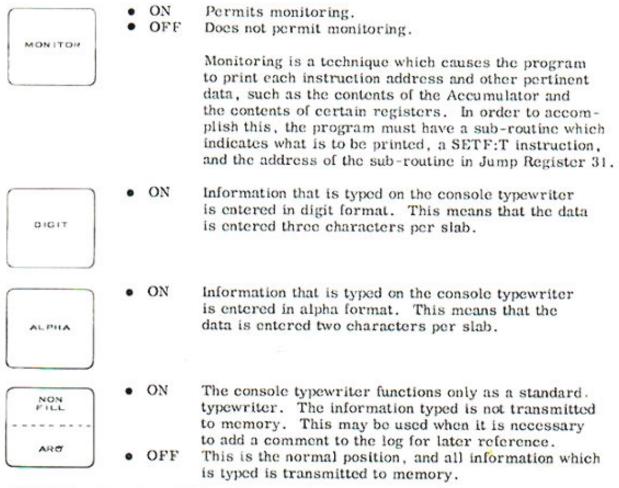

#### Control Buttons

The Control Buttons are located above the typewriter keys. Press the button to set it ON. The button may be set OFF by pressing it again. The ON condition is indicated by the button being lighted.

<sup>\* 315-100 -</sup> A system which utilizes ARO will have an ARO button in place of the NON-FILL button on the console.

<sup>315-</sup>RMC - This is the ARO button on this processor ... (standard equipment)

| NEW<br>MAIN        | • 01 | Main memory may be accessed by entering an address.                                                                                                                                                                                    |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | • 01 | The auxiliary memory may be accessed. This mem-                                                                                                                                                                                        |

| NEW                |      | ory consists of the Accumulator, the Index Registers and the Jump Registers.                                                                                                                                                           |

| NEW<br>START       | • O1 | The Processor is ready to receive a new starting address of the present program. This address will be placed in Index Register 31.                                                                                                     |

| PRINT              | • ON | The typewriter will print data which was received from the Processor.                                                                                                                                                                  |

|                    |      |                                                                                                                                                                                                                                        |

| COMPUTE            | • ON | When the button is pressed, the program will begin computing at the address which is presently in Index Register 31.                                                                                                                   |

| MALT               | • ON | The Processor halts upon completion of the current instruction.                                                                                                                                                                        |

| REST               | • ON | The Processor is in the REST state. This means that the Processor is still operational, but awaiting action by the operator. After the Processor is halted, it must be placed in REST before any of the other buttons may be utilized. |

| OPTION<br>SWITCHES | • ON | These option switches exercise control when the con-<br>ditions of the TEST:SW instruction in the object pro-<br>gram are met.                                                                                                         |

|                    |      |                                                                                                                                                                                                                                        |

ON Input to the Processor is to be punched paper tape. TAPE Input to the Processor is to be punched cards. ON CARD ON Conditions the Processor to be ready to read punched cards or punched paper tape when the COMPUTE button is pressed. To read a reel of punched paper LOAD tape, press TAPE, LOAD, COMPUTE. To read a deck of punched cards, press CARD, LOAD, COM-PUTE. Processor ON and OFF buttons ON These buttons are located to the right of the console, and control the power supply to the Processor and Console. OFF

#### Console Indicators

The Console Indicators display the status of the Processor. They are of visual aid during the REST or HALT stage. The console indicators are divided into the following elements:

- Status

- Main Memory

- Control

- Auxiliary Memory

- Input-Output

# Console Indicators

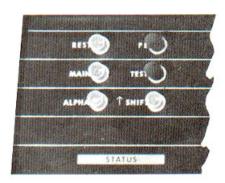

# Status Indicators

| REST       | • ON  | The Processor is in the REST state. The indicator is illuminated when the REST button is pressed.                     |

|------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| MAIN       | • ON  | Main memory may be accessed. The indicator is illuminated when the NEW MAIN button is pressed.                        |

| O<br>ALPHA | • ON  | Information entered is in the alpha format. The indicator is illuminated when the ALPHA button is pressed.            |

| PE         | • ON  | There is a Program Error.                                                                                             |

| O<br>TEST  | • ON  | The Processor is in an engineering test mode and internally stored programs can not be executed.                      |

| SHIFT      | • ON  | The console typewriter is in the upper shift position. The indicator is illuminated when the SHIFT button is pressed. |

|            | • OFF | The console typewriter is in the lower shift position.                                                                |

Status Indicators

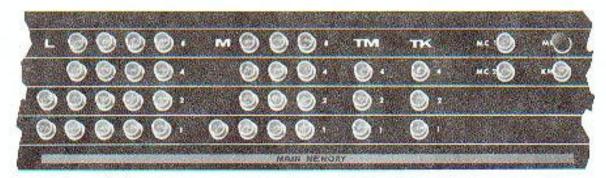

#### Main Memory Indicators

Main Memory Indicators

#### L Indicators

The L Indicators display the next Main Memory address. (If stepping through the program with the halt button depressed the address of the next command in sequence is displayed). In case of a Halt instruction, the "L" register contains the contents of XA address (Fill address).

If Main Memory is being accessed, the L Indicators display the next address into which data is to be entered or the next address from which data is to be printed.

The indicators are read from left to right, one column at a time. Each column represents a decimal digit. The right column is the least significant digit.

The address 29873 is displayed:

The address 00806 is displayed:

#### M Indicators

The M Indicators display the contents of the current main memory address while the program is running. These indicators are not significant since they are set to zero when the program halts.

However, the M indicators are read from left to right, one column at a time. Each light represents a bit; the M-register lights store 12 bits which can be two alpha-numeric characters or three digits. The 13th left-most bit represents the parity bit which is stored automatically. In example C, two alpha characters (AB) are represented in binary form as AB = 010001 010010. Reduced further into digit format as in the M indicators, AB = 0100 0101 0010. Therefore, characters AB appear in the M-register as shown in example C.

## TM Indicators

These indicators display the number of the peripheral unit which was selected in the program. If the program halts because of an incorrect peripheral setting, the operator may compare the unit number setting with the unit number displayed in the TM Indicators.

## TK MC1 MC2 Indicators

These indicators are used for maintenance purposes only.

ON A slab having incorrect parity is read into or from main memory. Pressing REST causes the Processor to again become operational, but this procedure does not correct the parity error.

ON The result of the last arithmetic operation was negative.

## Control Indicators

Control Indicators

The N COMMAND and N BLOCK Indicators are read from left to right, one column at a time. Each column represents an octal digit. The right column is the least significant digit. The number 7 is the maximum digit which can be displayed in octal format. For example:

| 000 | •   | Represents the number | 3  |

|-----|-----|-----------------------|----|

| 000 | 0   | Represents the number | 7  |

| 000 | 0 0 | Represents the number | 10 |

#### N COMMAND

These indicators display the instruction in octal digit format. The operation Codes and their representations are on the following pages.

#### N BLOCK

These indicators display the next micro block of the instruction which is indicated by the N COMMAND indicators,

#### Single Stage Instruction

The F portion of a single stage instruction is not displayed in the indicators. For example; if the instruction is LOAD (an operation code of 1) and the micro block is 3, the indicators will appear as:

| COMMAND         | BLOCK |

|-----------------|-------|

| 0<br>0 0<br>0 • | 0 0   |

| INSTRUCTIONS                                                                                                                                  | OP CODES<br>F C                                         | CONTENTS OF<br>N COMMAND<br>INDICATORS                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------|

| LOAD STORE ADD SUBTRACT MULTIPLY COMPARE TEST INSTRUCTIONS SHIFT INSTRUCTIONS ADD TO MEMORY BINARY ADD DIVIDE JUMP INSTRUCTIONS EDIT SUPPRESS | 1<br>2<br>3<br>4<br>5<br>6<br>0-7<br>0-7<br>8<br>9<br>@ | 01<br>02<br>03<br>04<br>05<br>06<br>07<br>10<br>11<br>12<br>13<br>14<br>15 |

|                                                                                                                                               |                                                         |                                                                            |

Single Stage Instructions

#### Double Stage Instruction

The Operation Codes zero (0) and hyphen (-) and the F portion of a double stage instruction are displayed in the N COMMAND Indicators. If the Operation Code is 0 it will appear as a 2 in the left column of the indicators. The value of the F portion appears in the right column. For example; if the instruction is LOAD ALPHA TO DIGIT (an operation code of 0 and an F of 5) and the micro block is 10, the indicators will appear as:

| COM | MAND | $_{\mathrm{BL}}$ | оск |

|-----|------|------------------|-----|

| •   | _    | 0                | _   |

If the Operation Code is hyphen (-) it will appear as a 3 in the left column of the indicators. The value of the F portion appears in the right column. For example; if the instruction is PRNT (an operation code of - and an F of 3) and the micro block is 6, the indicators will appear as:

| COMMAND | BLOCK |

|---------|-------|

| О       | 0     |

| • •     | 0     |

|         | 0.0   |

Listed here are the double stage instructions and their respective representations.

| INSTRUCTIONS                                     | OP C<br>F | ODES<br>C | CONTENTS OF<br>N COMMAND<br>INDICATORS |

|--------------------------------------------------|-----------|-----------|----------------------------------------|

| COUNT                                            | 1         | 0         | 21                                     |

| INDEX AND JUMP<br>REGISTER<br>MODIFICATION       | 2         | 0         | 22                                     |

| MOVE-SPREAD                                      | 3         | 0         | 23                                     |

| SCAN                                             | 4         | 0         | 24                                     |

| LOAD ALPHA-TO-<br>DIGIT                          | 5         | 0         | 25                                     |

| STORE DIGIT-TO-<br>ALPHA PARTIAL<br>ALPHA STORE  | 6         | 0         | 26                                     |

| SELECT - TEST SWITCH<br>SET AND CLEAR            | 7         | 0         | 27                                     |

| HALT - TYPE -<br>PUNCH PAPER TAPE                | 1         | -         | 31                                     |

| READ PAPER TAPE<br>READ CARDS                    | 2         |           | 32                                     |

| START - READ -<br>POCKET - STOP<br>PRINT - PUNCH | 3         | -         | 33                                     |

| MAGNETIC TAPE<br>INSTRUCTIONS                    | 4         | -         | 34                                     |

| CRAM INSTRUCTIONS                                | 5         | -         | 35                                     |

| INQUIRY INSTRUCTIONS                             | 6         | -         | 36                                     |

Double Stage Instructions

| 0  | • ON | Overflow has occurred. This may be the result of the program instruction SETF: which sets |

|----|------|-------------------------------------------------------------------------------------------|

| OF |      | the overflow flag ON, or it may be the result of                                          |

|    |      | an operation. The Processor will not halt unless                                          |

|    |      | the program specifies a halt.                                                             |

| ) | • | Various programming instructions or conditions may cause |

|---|---|----------------------------------------------------------|

| • |   | the Greater, Less, and Equal flags to be set ON. These   |

|   |   | indicators reflect the condition of these flags.         |

| U2  | Ul  | Flag Condition   |

|-----|-----|------------------|

| OFF | OFF | The G flag is ON |

| OFF | ON  | The L flag is ON |

| ON  | OFF | The E flag is ON |

| ON  | ON  | No flag is ON    |

| 0  | • ON | A Processor Control Error has occurred. It may<br>be an error in selecting the next micro block in |

|----|------|----------------------------------------------------------------------------------------------------|

| PG |      | sequence during the execution of an instruction,<br>or a malfunction which was introduced by pro-  |

|    |      | gramming errors.                                                                                   |

- ON The Demand Permit flag has been set ON in the program through the use of the instruction SETF:D.

- On The Monitor Permit flag has been set ON in the program through the use of the instruction SETF:T.

- This indicator is used for maintenance purposes only.

## T Indicators

These indicators are used for maintenance purposes only.

### Auxiliary Memory Indicators

Auxiliary Memory Indicators

Auxiliary memory consists of the Index Registers, the Jump Registers, and the Accumulator. Any part of Auxiliary memory may be interrogated and/or changed from the console.

The thirty-two index registers are numbered 0 through 31. They are internally divided into two groups of sixteen registers, each group being designated as Group 0 or Group 1. The thirty-two jump registers are numbered in the same manner.

|                |        |         |        |        | (IND    | ADD<br>DEX)<br>DISTER |                              |                   |              |     |    | JL<br>J—RE                                     | JMP<br>GISTE | RS                                                 |

|----------------|--------|---------|--------|--------|---------|-----------------------|------------------------------|-------------------|--------------|-----|----|------------------------------------------------|--------------|----------------------------------------------------|

| °4<br>0        | ·<br>• | 0       | 0      | 0      | 0       | 16                    | 0                            | 0                 | 0            | 0   | 0  | STEP uses Registers<br>00 through 05           | 16           | MICR Sorter-Reader uses<br>Registers 16 through 19 |

| 0              | ) ,    | 1       | 0      | 0      | 0       | 17<br><b>1</b>        | 1                            | 0                 | 0            | 0   | 1  |                                                | 17           |                                                    |

| 2              | ) ,    | 2       | 0      | 0      | 0       | 18                    | 2                            | 0                 | 0            | 0   | 2  |                                                | 18           |                                                    |

| 3<br>O         | ) ,    | 3       | 0      | 0      | 0       | 19                    | 3                            | 0                 | 0            | 0   | 3  |                                                | 19           | , , , , ,                                          |

| <sup>4</sup> O | )      | 4       | 0      | 0      | 0       | 20                    | 4                            | 0                 | 0            | 0   | 4  |                                                | 20           | Inquiry System uses<br>Registers 20 through 22     |

| <sup>5</sup> 0 | )      | 5       | 0      | 0      | 0       | 1                     | 5                            | 0                 | 0            | 0   | 5  | , , , ,                                        | 21           |                                                    |

| °              | )      | 6       | 0      | 0      | 0       | 1                     | 6                            | 0                 | 0            | 0   | 6  | CRAM EXECUTIVE user<br>Registers 06 through 11 | 22           | , , , ,                                            |

| <sup>7</sup> 0 | ) ,    | 7       | 0      | 0      | 0       | <sup>23</sup>         | 7                            | 0                 | 0            | 0   | 7  |                                                | 23           | ARO Link                                           |

| 8              | ) ,    | 8       | 0      | 0      | 0       | 3 ·                   | 8                            | 0                 | 0            | 0   | 8  |                                                | 24           | (ARO 1)                                            |

| °              | ) (    | 9       | 0      | 0      | 0       | <sup>25</sup>         | 9                            | 0                 | 0            | 0   | 9  |                                                | 25           | (ARO 2)                                            |

| 10             |        |         |        | 1      |         | 26                    |                              |                   |              |     | 10 |                                                | 26           | (ARO 3)                                            |

| ۱۱۱<br>ک       | ,      |         |        | 1      |         | 27                    |                              |                   |              |     | 11 | . ,                                            | 27           | Special Interrupt<br>Control                       |

| 12             |        |         |        |        |         | a                     | egister<br>re use<br>CRAM E  | d by S            | TEP,         |     | 12 |                                                | 28           |                                                    |

| 13             |        |         |        |        |         | 29 n                  | nacros<br>outines<br>ire not | and su<br>. Their | b-<br>conter | nts | 13 |                                                | 29           |                                                    |

| 14             |        |         |        |        |         | 30 P                  | rocesso<br>(Next             | r store:<br>addre |              |     | 14 | Jump-Table Link<br>(JY-Link)                   | 30           | Demand-Program Jump<br>Control                     |

| 15             | Ma     | in Link | (Progr | ram De | cision) | 31 5                  | Sequen                       |                   | -            |     | 15 | Demand-Program Link<br>(Auto-Link)             | 31           | Tracer-Program Jump<br>Control                     |

<sup>\*</sup>Class 407 uses 16 through 20

The table illustrated on the opposite page shows how index and jump registers may be accessed. For example.

The accessing addresses of Index Register 10 is @00.

- The @ represents the index register number in hexadecimal.

- The 0 represents Group 0 (i.e. the first fifteen index registers).

- The 0 means that this address relates to an index register.

The accessing address of Index Register 20 is 480.

- The 4 represents the fifth index register.

- The 8 signifies that this is Group 1.

- The 0 means that this address relates to an index register.

The accessing address of Jump Register 14 is .01.

- · The . represents the jump register number in hexadecimal.

- The 0 represents Group 0 (i.e. the first fifteen jump registers).

- The 1 means that this address relates to a jump register.

#### A Indicators

The A Indicators display the Auxiliary Memory address octally. This may be the address where the program has halted; or if auxiliary memory is being accessed, the address into which data is to be entered or the address from which data is to be printed.

The indicators are read from left to right, one column at a time. Each column represents a decimal digit. The right column is the least significant digit.

The A Indicators show which index or jump register is being accessed In the previous example of accessing Index Register 20, the A indicators would display:

| Effective<br>Length | Address<br>Typed | A<br>Indicator | rs                      |

|---------------------|------------------|----------------|-------------------------|

| 1 slab @            | 702              | 117            | (least significant end) |

| 2 slab @            | 602              | 116            |                         |

| 3 slab @            | 502              | 115            |                         |

| 4 slab @            | 402              | 114            |                         |

| 5 slab @            | 302              | 113            |                         |

| 6 slab @            | 202              | 112            |                         |

| 7 slab @            | 102              | 111            |                         |

| 8 slab @            | 002              | 110            |                         |

Accumulator Addressing Table

#### INDEX REGISTERS

#### JUMP REGISTERS

|    | Group<br>(IR 0 th) |                      | Grou<br>(IR 16 th |                       | Grou<br>(JR0 th)  |                      | Gro<br>(JR16 th   |                      |    |

|----|--------------------|----------------------|-------------------|-----------------------|-------------------|----------------------|-------------------|----------------------|----|

|    | Access<br>Address  | A<br>indi-<br>cators | Access<br>Address | A<br>indi –<br>cators | Access<br>Address | A<br>indi-<br>cators | Access<br>Address | A<br>indi-<br>cators |    |

| 0  | 000                | 000                  | 080               | 020                   | 001               | 040                  | 081               | 060                  | 16 |

| 1  | 100                | 001                  | 180               | 021                   | 101               | 041                  | 181               | 061                  | 17 |

| 2  | 200                | 002                  | 280               | 022                   | 201               | 042                  | 281               | 062                  | 18 |

| 3  | 300                | 003                  | 380               | 023                   | 301               | 043                  | 381               | 063                  | 19 |

| 4  | 400                | 004                  | 480               | 024                   | 401               | 044                  | 481               | 064                  | 20 |

| 5  | 500                | 005                  | 480               | 025                   | 501               | 045                  | 581               | 065                  | 21 |

| 6  | 600                | 006                  | 680               | 026                   | 601               | 046                  | 681               | 066                  | 22 |

| 7  | 700                | 007                  | 780               | 027                   | 701               | 047                  | 781               | 067                  | 23 |

| 8  | 800                | 010                  | 880               | 030                   | 801               | 050                  | 881               | 070                  | 24 |

| 9  | 900                | 011                  | 980               | 031                   | 901               | 051                  | 981               | 071                  | 25 |

| 10 | @00                | 012                  | @30               | 032                   | @01               | 052                  | @81               | 072                  | 26 |

| 11 | ,00                | 013                  | ,80               | 033                   | ,01               | 053                  | ,81               | 073                  | 27 |

| 12 | ⊄00                | 014                  | <b>⊠</b> 80       | 034                   | Ø 01              | 054                  | Ø81               | 074                  | 28 |

| 13 | &00                | 015                  | &80               | 035                   | &01               | 055                  | &81               | 075                  | 29 |

| 14 | .00                | 016                  | .80               | 036                   | .01               | 056                  | .81               | 076                  | 30 |

| 15 | -00                | 017                  | -80               | 037                   | -01               | 057                  | -81               | 077                  | 31 |

Index and Jump Register, Addressing Tables

In the example of accessing Jump Register 14, the A Indicators would display:

The Accumulator is an eight slab working area which is used to hold the results of all arithmetic operations, and to store alpha or digit characters as a result of certain instructions. The effective length of the Accumulator is the left most non-zero slab of the Accumulator. For example, in the following instance, the effective length is five.

|     |     | ١   | /   |     |     |     |     |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 000 | 000 | 000 | 831 | 000 | 006 | 321 | 794 |  |

The illustration on the opposite page shows the relative positions of the Accumulator, the accessing addresses, and the digit representations in the A Indicators. If the third relative position of the previous example is to be typed, the accessing address is 502. The A Indicators would display:

The console typewriter would print:

Note that the third position of the Accumulator contains 006. When entering information into the Accumulator, one slab is filled at a time until slab 117 is filled. When interrogating the Accumulator, the contents of the address accessed and the contents of the remaining slabs to the right are printed.

## S Indicators

The S Indicators display the contents of the auxiliary memory address. The indicators are read from left to right, one column at a time. The right column is the least significant digit. The left column contains a parity bit. For example, if the contents of an index register were 21678, the S Indicators would display:

If the contents of a jump register were 05353, the S Indicators would display:

The least significant digit of the assigned address of the first slab of the effective length of the Accumulator. Illustrated below is an Accumulator which has the effective length of three slabs. The assigned address of the third position of 115. The 5 (least significant digit) would be displayed in the T@ Indicator. To determine the effective length of the Accumulator, subtract the digit which is displayed from the number 8. The result is the effective length.

|                   |      |     |     |     | -   |     |                |     |

|-------------------|------|-----|-----|-----|-----|-----|----------------|-----|

| Relative position | 8    | 7   | 6   | 5   | 4   | 3   | 2              | 1   |

| Address           | 110  | 111 | 112 | 113 | 114 | 115 | 116            | 117 |

|                   |      |     |     |     |     |     |                |     |

| Applying the form | nlo. |     |     |     |     | 100 | fecti<br>engtl |     |

Applying the formula:

$$8 - 5 = 3$$

Data having incorrect parity has been read from auxiliary memory.

ON The sign of the Accumulator is negative.

These indicators are used for maintenance purposes only.

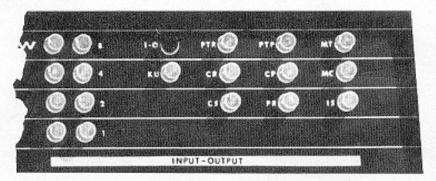

## Input-Output Indicators

Input-Output Indicators

## W Indicators (used on 315 only)

- ON The indicators display data which has been transferred to or from peripheral units.

- O ON A buffered peripheral or CRAM unit has malfunctioned.

- ON A peripheral unit has its Unit Demand Flag ON, and is in the READY state.

- ON Input is being received from the Paper Tape Reader.

- ON Input is being received from a Card Reader.

- O ON Input is being received from a Document Sorter-Reader.

# Processor Hang-up and Halt Situations

- 27-05: Error Halt for literals or unspecified modes.

- 27-11: Hang-up if more than one CRAM Unit assigned same unit number.

- 27-12:

Hang-up if more than one print/punch Buffer assigned same unit number.

- 27-13: Hang-up if more than one Check Sorter Buffer assigned same unit number.

- 27-14: Hang-up if more than one Inquiry Station Buffer assigned same unit number.

- 27-16: Hang-up if Unit Interrupt Indication will not clear in selected buffer.

- 27-17: Hang-up if Unit Interrupt Indicator will not set in selected buffer.

- 27-24: Hang-up if Select Indicator will not clear.

- 27-25: Hang-up if Select Indicator will not set.

- 27-31: Hang-up if CRAM Select Indicator will not clear.

- 27-32: Hang-up if CRAM Select Indicator will not set.

- 27-35: Hang-up if CRAM partially dropped card (hanger).

- 27-36: Hang-up if CRAM partially dropped card (hanger).

- 27-45: Hang-up if CRAM card not released from drum.

- \*Command (N-Register) and Block number associated with Processor Hang-up and Halt situations.

31-04: Error Halt if literal or unspecified modes. 31-12: Hang-up waiting for go-ahead from either the output-writer or paper tape punch (allow for mechanical sync). 31-13: Hang-up waiting for go-ahead from output-writer (allow for mechanical sync). 31-15: Same as Block 13. 31-16: Hang-up waiting for go-ahead from output-writer. 31-24: Hang-up waiting for go-ahead from output-writer. 32:04: Error Halt if literal or mode not specified. 32-07: Hang-up waiting for clock (generated by sprocket hole) from paper tape reader. 32-10: Hang-up, can't read data - tape reader malfunction or photo cell out (PTR). 32-11: Hang-up, can't read data (PTR). 32-12: Hang-up if tape malfunction or photo cell out (PTR). 32-32: Hang-up waiting for data clock from card reader. 32-33: Hang-up, can't read data - card reader malfunction or photo cell out (CR). 33-04: Error Halt for literal and undefined modes. 33-05: Error Halt if no unit selected. 33-07: Hang-up if Check Sorter ready line not true. 33-11:

Hang if Check Sorter buffer busy.

1) Write status set and read command issued.

2) Tape positioned on trailer.

Error Halt if tape positioned on trailer.

Hang-up, wait for Write Status to be set.

Error Halt if,

34-17:

34-24:

34-25:

- 34-30: Hang-up, wait for beginning of information marker to be seen.

- 34-34: Hang-up, wait to write check sum.

- 34-35: Hang-up, waiting for inter-block gap to be erased.

- 34-36: Hang-up, wait for beginning of information marker to be seen.

- 34-52: Hang-up, until complete block is read.

- 34-53: Hang-up, wait for sum check to be read and checked.

- 34-64:

Hang-up, waiting for tape to get up to speed (forward).

- 34-66:

Error Halt if on Load Point or Leader, and command is Index Backwards.

- 34-70: Hang-up, waiting for tape to get up to speed (reverse).

- 34-71: Hang-up, wait for first character when reversing.

- 34-72:

Hang-up, wait until you have backed up to the beginning of the block.

- 34-73: Hang-up, wait until unit starts to rewind.

- 34-74: Hang-up, wait until Use Lockout Set.

- 35-04: Error Halt for unspecified modes.

- 35-05: Error Halt if unit not selected.

- 35-10: Hang-up, wait for channel No. echo.

- 35-12: Error Halt if 'N' is greater than 1999.

- 35-13: Error Halt if three least significant digits of 'N' are > 550.

- 35-25: Hang-up, waiting to go ahead for read or write operation.

- 35-27:

Hang-up, waiting for lead edge of card to be erased before write operation can begin.

- 35-33: Hang-up, waiting to write check sum.

- 35-35: Hang-up, wait for first character written to reach read head.

- 35-36: Hang-up, wait for lead edge of card to pass read head.

- 35-52: Hang-up, wait until all characters are read including the check sum.